# From Design Space Exploration to Code Generation

a constraint satisfaction approach for the architectural synthesis of digital VLSI circuits

# **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr. J.H. van Lint, voor een commissie aangewezen door het College van Dekanen in het openbaar te verdedigen op woensdag 3 april 1996 om 16.00 uur

door

Adwin H. Timmer

geboren te Apeldoorn

Dit proefschrift is goedgekeurd door de promotoren:

prof.Dr.-Ing. J.A.G. Jess

en

prof.dr. E.H.L. Aarts

en door de copromotor:

dr. ir. M.R.C.M. Berkelaar

CIP-gegevens Koninklijke Bibliotheek, Den Haag

Timmer, Adwin H.

$From \ Design \ Space \ Exploration \ to \ Code \ Generation: a \ constraint \ satisfaction \ approach \ for \ the \ architectural \ synthesis \ of \ digital \ VLSI \ circuits$

Proefschrift Technische Universiteit Eindhoven. – Met lit. opg. – Met samenvatting in het Nederlands.

ISBN 90-74445-24-1

Trefw.: architectural synthesis, code generation, constraint satisfaction.

voor mijn vader

Je m'appelle Zangra Et je suis Lieutenant Au fort de Belonzio Qui domine la plaine D'où l'ennemi viendra Qui me fera héros

$Jacques\ Brel\ (Zangra,\ 1962)$

v

# Summary

Ongoing technological developments result in the design and fabrication of increasingly larger and more complex electronic systems compared with the systems that are currently in use. For a short design cycle and time to market, good design methodologies for the computer—aided design (CAD) of these systems are very important. The need for productivity has initiated the development of *architectural* (or *high-level*) *synthesis* methods. This thesis deals with such methods, which have been developed at the Design Automation Section of the Eindhoven University of Technology.

Architectural synthesis tools take an algorithmic description with goals and constraints as their input, and produce a register transfer level description of an IC architecture as their output. A major part of such a description is the datapath, which consists of interconnected basic building blocks like adders, multipliers, memories etc. Three main tasks can be distinguished when synthesizing a datapath: resource selection, scheduling and binding. The organization of these interdependent subtasks can influence the quality of the result substantially, and might depend on the application domain as well. The three individual tasks are in general not solvable in polynomial time, thus leading to numerous heuristical solution methods.

Most architectural synthesis methods can only take a limit number of different kinds of constraints into account. Such constraints can either be part of the initial problem description, or can be formulated during the design flow. Furthermore, they can be related to timing, resources, specific bus architectures, etc. So, most methods concentrate on minimizing one or a few objective functions, e.g., the chip area requirements. The synthesis result is then checked against other constraints that were not yet taken into account. However, this often leads to unsatisfactory results, because the synthesis result often does not comply with the other constraints, especially when they are tight.

For that reason, *constraint satisfaction* techniques are emphasized in this thesis. In our approach, a designer can modify the initial problem description interactively by adding new constraints or by enforcing certain design decisions. In this way, a trade–off can be made between the quality of a solution and the run time efficiency.

The central theme in this thesis is a new algorithm based on a graph formulation, namely the so called 'bipartite schedule graphs' (BSGs). The algorithm advances the ability of synthesis systems to deal with combinations of timing and resource constraints, rather than being hampered by them. The BSGs are applied in two different ways.

First, the BSGs prune the search space of schedulers, which is called *domain reduction*. Classical operation execution intervals are usually obtained by a critical path analysis under the assumption of unlimited resources. The BSGs, however, take the timing, precedence and resource constraints into account, which leads to a reduction of the execution intervals. This results in a reduction of the search area as well, but does not affect the solution space at all.

Secondly, the BSGs are used to identify the 'bottlenecks' for a scheduler. Those bottlenecks typically fool heuristic methods (because they are not recognized by such methods), and they are a source of wasted search effort for exact schedulers. The BSGs identify the bottlenecks and consequently make an efficient *traversal of the search space* possible, because the bottlenecks are solved first.

The domain reduction and scheduling methods not only prove their value in the field of architectural synthesis, but also in other situations in which the constraints are very tight, such as (retargetable) code generation. A solution strategy is proposed in which code generation is the last step in the architectural synthesis flow. The complete datapath with timing constraints is fixed in the case of code generation, so the remaining task is to find a correct schedule and binding scheme. Industrial examples show that the methods described in this thesis lead to an efficient code generation approach, thus validating the proposed methodology.

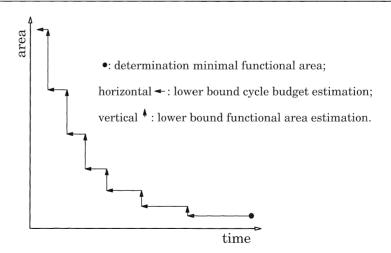

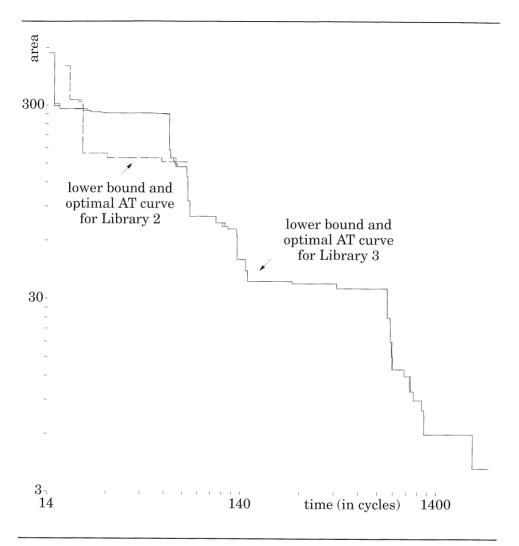

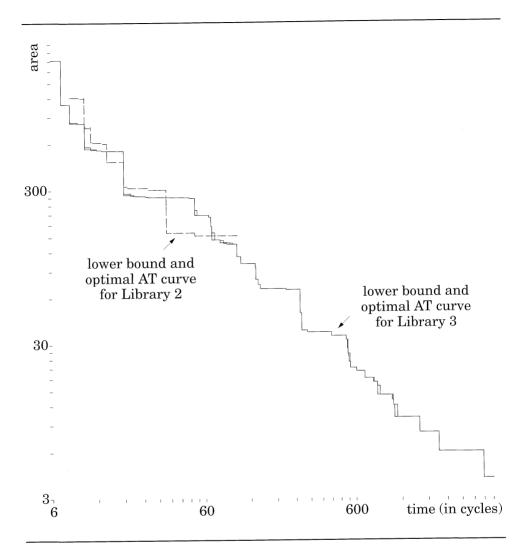

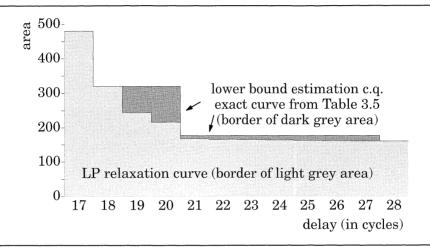

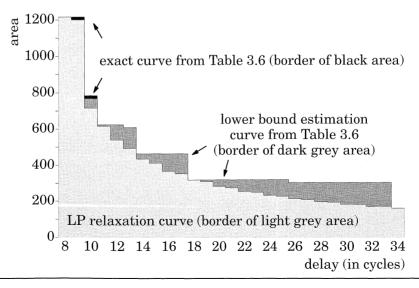

Last but not least, the methods can be applied for lower bound analyses. These analyses can help CAD tools, they can help to make interactive design decisions, and they can help to impose extra constraints during the synthesis flow. Furthermore, such analyses give a good insight in the design space, so they can help to measure the quality of a design as well. In this thesis, lower bound analyses related to functional area and cycle budget are presented. It is shown that the analyses are more accurate than other lower bound analyses that run in polynomial time. Furthermore, the only existing method capable of performing an efficient lower bound estimation for non-trivial module libraries is presented as well.

# Samenvatting

Door de voortschrijdende technologische ontwikkelingen kunnen steeds ingewikkeldere elektronische systemen ontworpen en gebouwd worden. Goede, computerondersteunde ontwerpmethoden zijn daarbij onontbeerlijk. Zij moeten ervoor zorgen dat de ontwerptijd kort is, zodat ook de tijd tussen de specificatie en de marktintroductie van een systeem kort is. Deze hoge productiviteitseis heeft geleid tot de ontwikkeling van architectuur—(of hoogniveau) synthese—methoden. Dit proefschrift beschrijft nieuwe architectuur—synthese—methoden, die ontwikkeld zijn in de vakgroep Ontwerpkunde voor Elektronische Systemen van de Technische Universiteit Eindhoven.

Het belangrijkste onderdeel van de architectuur-synthese is de vorming van het datapad. Het datapad is de basis van de IC architectuur op registerniveau, het eindresultaat van de synthese. Het bestaat uit bouwblokken, zoals optellers, vermenigvuldigers en geheugenelementen, die onderling verbonden zijn. Invoer voor de synthese van het datapad is een algoritmische beschrijving waarvoor beperkingen en doelstellingen zijn geformuleerd. Bij de synthese van het datapad onderscheidt men drie taken: de selectie van de bouwblokken, de tijdstoewijzing van operaties en de afbeelding van de operaties op de bouwblokken. De volgorde en invulling van deze taken kunnen een grote invloed hebben op het uiteindelijke resultaat, en kunnen tevens afhangen van het toepassingsgebied. Deze drie taken zijn in het algemeen niet in polynomiale tijd oplosbaar. Daarom is er voor het oplossen van deze taken veel aandacht voor benaderingsmethoden.

De gangbare architectuur—synthese—methoden kunnen slechts in beperkte mate rekening houden met beperkingen die deel uitmaken van de invoer of die tijdens het ontwerptraject geformuleerd worden. Deze beperkingen kunnen te maken hebben met tijdsaspecten, bouwblokken, specifieke bus architecturen of andere aspecten van het ontwerp. De gangbare methoden gaan uit van de algoritmische beschrijving en concentreren zich op het minimaliseren van bepaalde kostenfuncties, bijvoorbeeld het benodigde chip—oppervlak. Het zoekresultaat wordt vervolgens getoetst aan de hand van de overige beperkingen. Dit levert vaak een onbevredigend resultaat op, omdat vaak niet aan de overige beperkingen wordt voldaan, zeker in situaties waarin de beperkingen zeer streng zijn.

De methoden die in dit proefschrift worden beschreven nemen juist de beperkingen als uitgangspunt voor het syntheseproces. Naast de beperkingen uit de initiële specificatie kan de gebruiker in interactie met het systeem beperkingen toevoegen of ontwerpbeslissingen afdwingen. Hierdoor kan een afweging gemaakt worden tussen de kwaliteit van de oplossing en de snelheid waarmee de oplossing wordt bereikt.

Kernpunt van de in dit proefschrift beschreven methodiek is een nieuw algoritme dat gebaseerd is op een graaf-formulering, de bipartiete tijdstoewijzings graaf BSG ('bipartite schedule graph'). De BSG brengt de synthese-opgave in kaart en heeft de volgende twee functies.

In de eerste plaats reduceert de BSG de zoekruimte van de tijdstoewijzing, hetgeen domein reductie genoemd wordt. Klassieke executie intervallen van operaties worden verkregen door een kritieke pad analyse, waarbij dan aangenomen wordt dat er een onbeperkt aantal bouwblokken beschikbaar is. De BSG neemt echter de beperkingen ten aanzien van de tijd, precedenties en het aantal en soort bouwblokken in de beschouwing mee, en hierdoor kan een deel van de opties buiten beschouwing gelaten worden. De zoekruimte wordt hierdoor verkleind, de oplosruimte echter niet.

De tweede functie van de BSG is de identificatie van knelpunten in de tijdstoewijzing. Gangbare methoden hebben hier moeite mee: heuristische methoden herkennen de knelpunten niet, terwijl exacte methoden er teveel tijd voor nodig hebben. De BSG identificeert de knelpunten en maakt het vervolgens mogelijk de zoekruimte efficiënt te doorlopen, doordat allereerst de knelpunten worden opgelost.

Behalve in de architectuur-synthese bewijzen de beschreven methoden ook hun waarde in andere situaties waarin de beperkingen zeer streng zijn, zoals bij code-generatie. In dit proefschrift wordt een ontwerpstrategie voorgesteld, waarbij de code-generatie een losse synthese-stap aan het eind van het architectuur-synthese-traject is. Het complete datapad met tijdsbeperkingen ligt in het geval van code-generatie vast, en de enige overgebleven taak is een correcte tijdstoewijzing van de operaties te vinden en een correcte afbeelding van de operaties op de bouwblokken. Industriële voorbeelden tonen aan dat de methoden gepresenteerd in dit proefschrift tot een efficiënte en doelmatige code-generatie leiden.

Ten slotte zijn de beschreven methoden toepasbaar voor ondergrensanalyses t.b.v. CAD-gereedschappen of interactieve ontwerpbeslissingen. Deze analyses kunnen gebruikt worden voor het bepalen van extra beperkingen die tijdens het ontwerptraject opgelegd kunnen worden. Bovendien leveren ze een goed inzicht in de ontwerpruimte op, waardoor ze behulpzaam zijn bij het vaststellen van de kwaliteit van een ontwerp. In dit proefschrift worden ondergrens—analyses gepresenteerd voor de functionele oppervlakte en voor het tijdsbudget van een ontwerp. Er wordt aangetoond dat de beschreven methoden nauwkeuriger zijn dan andere polynomiale analyses. Verder wordt ook een methode gepresenteerd die als enige bestaande methode in staat is om een efficiënte ondergrens—analyse te doen voor niet—triviale module—bibliotheken.

# **Contents**

|   | Summary                                        | v  |

|---|------------------------------------------------|----|

|   | Samenvatting                                   | i  |

|   | Contents                                       | xi |

|   | Preface                                        | X  |

| 1 | Architectural Synthesis                        |    |

|   | 1.1 Introduction                               |    |

|   | 1.2 The design flow of silicon compilers       |    |

|   | 1.3 A design methodology                       |    |

|   | 1.3.1 The classical problem decomposition      |    |

|   | 1.3.2 VLSI design considerations               |    |

|   | 1.3.3 The proposed methodology                 |    |

|   | 1.3.4 Methodology considerations               |    |

|   | 1.4 Towards a solution strategy                |    |

|   | 1.5 Description of the NEAT design environment |    |

|   | 1.5.1 Overview of requirements                 |    |

|   | 1.5.2 NEAT and its data domains                |    |

|   | 1.5.3 Design relations                         |    |

| 2 | Execution Interval Analysis                    | ]  |

|   | 2.1 Introduction                               |    |

|   | 2.2 Definitions                                |    |

|   | 2.3 Trivial module sets                        | 6  |

|   | 2.3.1 Overview                                 | 9  |

|   | 2.3.2 Module execution intervals               | 6  |

|   | 2.3.3 Bipartite graph matching formulation     | ;  |

|   | 2.3.4 BSG arcs                                 |    |

|   | 2.3.5 Run time complexity                      | ;  |

|   | 2.3.6 Additional analyses                      | 4  |

|   | 2.4 Unrestricted module sets                   | 4  |

|   | 2.4.1 Bipartite schedule graph definition      | 4  |

|   | 2.4.2 Module execution intervals               | •  |

|   | 2.5 Experiments and results                    |    |

|   | 2.6 Discussion                                 |    |

| 3 | Lower Bound Analyses                                         | 49       |

|---|--------------------------------------------------------------|----------|

|   | 3.1 Introduction                                             | 49       |

|   | 3.2 Related work                                             | 50       |

|   | 3.3 Lower bound cycle budget estimation                      | 51       |

|   | 3.4 Lower bound functional area estimation                   | 53       |

|   | 3.4.1 Introduction                                           | 53       |

|   | 3.4.2 Trivial module libraries                               | 53<br>54 |

|   | 3.4.4 Distribution constraints                               | 55<br>55 |

|   | 3.4.5 Fixed operation constraints                            | 60       |

|   | 3.4.6 Path delay constraints                                 | 61       |

|   | 3.5 Reviewing infeasible module sets                         | 62       |

|   | 3.5.1 Detection in case of COEIs                             | 62       |

|   | 3.5.2 Detection in case of reduced OEIs                      | 63       |

|   | 3.6 Efficient lower bound AT curve prediction                | 64       |

|   | 3.7 Experiments and results                                  | 65       |

| 4 | Scheduling                                                   | 71       |

|   | 4.1 Introduction                                             | 71       |

|   | 4.2 Scheduling based on bipartite schedule graphs            | 73       |

|   | 4.2.1 Problem formulation                                    | 73       |

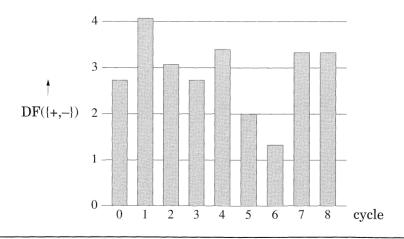

|   | 4.2.2 Bottleneck identification                              | 75<br>79 |

|   | 4.3 Scheduling based on integer linear programming           | 79<br>79 |

|   | 4.3.2 Evaluation of time vs. resource constrained scheduling | 81       |

|   | 4.3.3 Enhancements of the IP model                           | 84       |

|   | 4.4 Experiments and results                                  | 88       |

| 5 | Retargetable Code Generation                                 | 91       |

| - | 5.1 Introduction                                             | 91       |

|   | 5.2 Modelling resource and instruction set conflicts         | 93       |

|   | 5.2.1 Register transfer generation                           | 93       |

|   | 5.2.2 Resource conflicts                                     | 95       |

|   | 5.2.3 Instruction set conflicts                              | 96       |

|   | 5.3 Instruction scheduling based on BSGs                     | 98<br>98 |

|   | 5.3.1 Background                                             | 99<br>90 |

|   | 5.3.3 Definitions                                            | 100      |

|   | 5.3.4 Module execution intervals                             | 102      |

|   | 5.3.5 Construction of BSGs per resource                      | 103      |

|   | 5.3.6 Construction of BSGs per clique of RTs                 | 108      |

|   | 5.4 Experiments and results                                  | 110      |

| 6 | Conclusions and Discussion                                   | 115      |

|   | References                                                   | 119      |

|   | Notation                                                     | 125      |

|   | Biography                                                    | 131      |

# **Preface**

# Organization of this thesis

We start this thesis with a short overview of architectural synthesis and related topics in Chapter 1. The design methodology and strategy, on which the algorithms in this thesis are based, are explained in that chapter as well. In Chapter 2, the central theme of the thesis is presented: execution interval analysis based on bipartite schedule graphs. That chapter can be read in isolation. The rest of the thesis is (partly) based on that chapter and can therefore not be read in isolation.

In Chapter 3, lower bound analyses for the functional area and the cycle budget of a design are given. In Chapter 4, exact scheduling approaches are discussed. That chapter can be read without reading Chapter 3. In Chapter 5, the methods of Chapter 2 and 4 are applied on the code generation problem. That chapter can therefore also be read without reading Chapter 3. Note that the most important notations can be found at the end of this book.

# Acknowledgements

First of all, I would like to express my gratitude to Prof. Jochen Jess, for the opportunity to work on my Ph.D. thesis in his research group. His, albeit often indirect, influence on my education has undoubtedly been very large. Secondly, I would like to thank the NEAT club (Wim Philipsen, Ric Hilderink, Marc Heijligers and Harm Arts) for the fruitful cooperation on architectural synthesis tools. Furthermore, I owe a lot to Leon Stok, who gave me a very good start—up on the subject.

I would like to thank my two roommates at the university, Ronald Tangelder and Koen van Eijk, for being the perfect sounding boards for me. I would also like to thank the M.Sc. students, Paul Gruijters, Henry Faber and Joost van Leeuwen, as well as the trainee students who participated in the development of the methods presented in this thesis. I am also very indebted to my copromotor Michel Berkelaar for his MILP solver, which I have been using extensively. I would like to thank all other members of the Design Automation Section of the Eindhoven University of Technology as well, for their stimulating discussions on various topics.

I am also very grateful for the cooperation with Marino Strik and Jef van Meerbergen from the Philips Nat.Lab. Without their personal involvement and their benchmarks, the research on code generation would never have taken place. I also want to thank the Philips Nat.Lab. for publishing my thesis in their series. Furthermore, I would like to thank my reading committee, and especially my second promotor Prof. Emile Aarts, for the valuable comments on the formulations in this thesis. Last but not least I want to thank Ine Waterreus and my family for their support and encouragements during the last years.

# Chapter

# 1 Architectural Synthesis

### 1.1 Introduction

Ongoing technological developments result in the design and fabrication of increasingly larger and more complex electronic systems than the systems that are currently in use. For a short design cycle and a short time to market, good design methodologies and tools for the computer—aided design (CAD) of these systems are very important. Tools for the *logic* and *layout synthesis* of integrated circuits (ICs) are therefore widely used nowadays. However, the ever increasing complexity and versatility of ICs pushes CAD methods to even higher abstraction levels. This has initiated the development of methods at the *architectural level* of an IC, and nowadays *system—level synthesis* and *hardware—software codesign* are already very popular research areas.

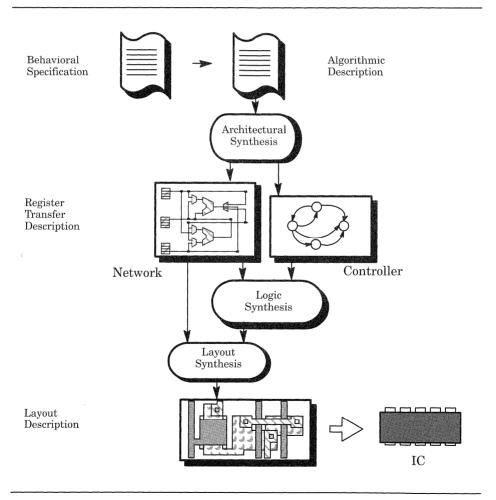

The overall system that helps in designing very large scale integrated (VLSI) circuits is called a *silicon compiler*. In Figure 1.1, a rough sketch of the design flow of such a compiler is depicted. This thesis is concerned with the *architectural synthesis* part of a silicon compiler for synchronous (clocked) VLSI circuits.

The organization of the remainder of this chapter is as follows. Section 1.2 starts with a short overview of the design flow of silicon compilers. The architectural synthesis methods presented in this thesis are based on the design methodology explained in Section 1.3. The design methodology results in the solution strategy for the synthesis of VLSI circuits described in Section 1.4. The design methodology, its synthesis strategy and other considerations lead to general requirements for an architectural synthesis system. Section 1.5 gives a short overview of the kernel of such a system developed at the Design Automation Section of the Eindhoven University of Technology.

# 1.2 The design flow of silicon compilers

The design flow of a silicon compiler starts either with a *behavioral specification* of the IC, or with an *algorithmic description* in a hardware description language like VHDL, Silage or HardwareC. A behavioral specification is an

abstract description of a circuit under construction. An example of such a specification is the transfer function of a digital filter. An algorithmic description is a slightly more detailed description when compared to a behavioral specification. An example is the description of a digital filter as an FIR (finite input response) or as an IIR (infinite input response) filter.

Most compilers require an algorithmic description to start with, although some research by [Raba93] and [Potk94] has been done to automate the translation of behavioral specifications into algorithmic descriptions. Such a description can, in general, also be the result of (automated) design steps preceding the design of an IC. Examples of such design steps are system—level synthesis and hardware—software codesign.

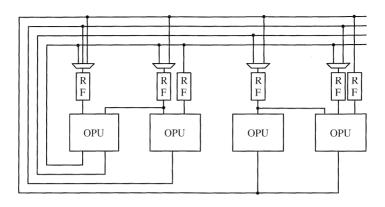

FIGURE 1.1. Computer-aided VLSI design flow, taken from [Stok91].

The architectural synthesis, also called high-level synthesis, tools take an algorithmic description together with goals and constraints as their input, and produce a so called register transfer level (RTL) description of a chip architecture. Such an architecture consists of a datapath, in the form of a network description, and a controller, in the form of a symbolic finite state machine. A datapath is a collection of basic building blocks like adders, multipliers, ALUs, shifters, memory elements etc., which are interconnected by buses and other interconnection units like (de-)multiplexers. The corresponding controller governs the data flow in the architecture. A comprehensive introduction on architectural synthesis and related research can be found in [McFa90].

Both the controller description and parts of the datapath are then fed to *logic* synthesis tools. These tools transform the RTL description into an implementation at the *gate level*. Logic synthesis includes the state encoding for the finite state machine, the optimization of logic blocks and the mapping onto a given technology. At this stage of the design process, modules in the datapath, like multipliers and ALUs, may be generated by module generators.

The final synthesis steps performed by the *layout synthesis* tools consist of layout design tasks such as *floor planning*, *placement* and *routing*. At this stage also the layout of basic building blocks like ROMs, RAMs, registers, basic logic cells, and regularly structured datapath components can be generated. The result is a set of geometrical descriptions of *layout masks*, which are a complete physical description of the IC under construction.

While layout and logic synthesis tools are widely used nowadays, true architectural synthesis is still working its way up from infancy. However, it can offer a lot of advantages due to its higher level of abstraction. The algorithmic description of an IC is a formal specification at a high level of the design process. The simulation of such a description allows a designer to evaluate the intended behavior of the design. The use of architectural synthesis methods can result in a shorter design cycle, it can enable a (system) designer to explore the design space more rapidly, and it can result in designs that contain fewer errors. The formal algorithmic description forces a designer to specify the design very precisely. Together with records kept by an automated design management, the result of the design process can be well documented.

Thus the objective of architectural synthesis is to support a designer at a higher level of abstraction than logic and layout synthesis do. Due to this level of abstraction and the possibility of better design space explorations, a designer should be capable of making better VLSI designs within a shorter amount of time.

# 1.3 A design methodology

# 1.3.1 The classical problem decomposition

In the previous section, the task of designing an electronic system or IC was decomposed into several subtasks. These subtasks are of course heavily interrelated but are hard to solve in their entirety. For the same reason, the architectural synthesis task is also decomposed into several subtasks. The first decomposition that is normally made is the decomposition into *datapath synthesis* and *controller synthesis*. It is very difficult to automate the trade–offs between datapath and controller costs, so most architectural synthesis systems do not design the datapath and controller of a VLSI circuit simultaneously. The following three main subtasks are generally distinguished when synthesizing a datapath from a behavioral description.

- Selection determines the type and number of resources needed for a datapath.

- *Scheduling* determines an assignment of the operations to be executed in the datapath to specific moments in time.

- *Binding* determines an assignment of the operations to specific resources.

Note that allocation is also a term that is heavily used in the literature. Unfortunately, the term is often used to identify different subtasks, e.g., selection only, selection and binding together, and so on. To avoid confusion, the term allocation is therefore not used in this thesis.

Many synthesis problems, like the subtasks mentioned above, are known to be NP-hard [Garey79] in general cases, see for instance [Verh95]. The organization of these interdependent subtasks influence the quality of the resulting datapath substantially. The way and order in which these subtasks are solved can depend on different application domains, e.g., micro processors versus digital signal processors or control-dominated designs versus datapath-dominated designs. These different application domains can require different optimization strategies to end up with good RTL designs.

Depending on the application, different goals and constraints, in terms of area, timing, power consumption, etc., are imposed by a designer, possibly leading to different synthesis strategies. So, one might raise the question whether an overall design methodology for all application domains can be constructed and whether it would be favorable. The answer to this question is contained in the following three elements of discussion.

# 1.3.2 VLSI design considerations

When choosing a VLSI design methodology, the following aspects must be considered.

- 1. In many cases the goal of the optimization for a design cannot be captured efficiently by means of a well defined objective function. For instance, many designs have only timing constraints at the beginning of the design process, and the optimization goal is to end up with a design with as little area as possible. However, it is almost impossible to model the interconnect costs and delays at high level. The cost of a bus or the signal delay can be very high if the modules connected by the bus are placed far away from each other by the layout synthesis tools. But they are (nearly) zero, if the modules are abutted. Counting the number of buses is therefore not a valid way to obtain a good measure for the interconnect costs and delays. On the other hand, evaluating all possible datapaths and bus configurations down to layout level to pick the best one is much too (CPU-) time consuming.

- **2.** Many optimization goals are hard to combine or even contradicting. For instance, the optimization goal for many designs is to end up with as small as possible power consumption and area. However, minimal area can imply a lot of multiplexing in the datapath, which in turn leads to a high power consumption. At many stages of the design process a choice has to be made as to the optimization goals to be pursued at that particular stage.

- 3. The constraints and goals imposed on an IC design are in most cases much stricter than for instance in the case of software compilation. Hard timing constraints imposed by the environment of an IC design have to be met by all means, while every square millimeter saved in terms of chip area can lead to important economical advantages. In the field of software compilation, the completion time of an algorithm is not that important in comparison with the hard constraints imposed on the throughput of, for instance, digital signal processing (DSP) applications. There are exceptions like [Chou94], but in that approach the resulting schedule is fully serial, so no parallelism in the datapath is possible. Such parallelism is usually needed in most architectural synthesis applications in order to obtain sufficient throughput. So, because the constraints and goals are quite strict in architectural synthesis, a designer wants to have thorough control over the design process and wants to be able to enforce synthesis decisions and strategies at his will.

The ultimate architectural synthesis system is one in which no user interaction is needed. However, this is still far away. There are many cases where a designer wants to outperform computer programs and seems to have the ability to do so. This means that user interaction remains important, also in the next generation(s) of architectural synthesis systems.

# 1.3.3 The proposed methodology

The discussion above shows that an architectural synthesis system cannot be steered by means of an objective function only. An efficient architectural synthesis objective function does not discriminate sufficiently between good and bad architectural solutions. Another solution methodology which is not solemnly based on optimizing objective functions has therefore to be found. Consider the case in which a solution is said to be good if and only if it satisfies the constraints imposed on a design problem, without considering some objective function. In such a case a synthesis system can easily discriminate between good and bad solutions.

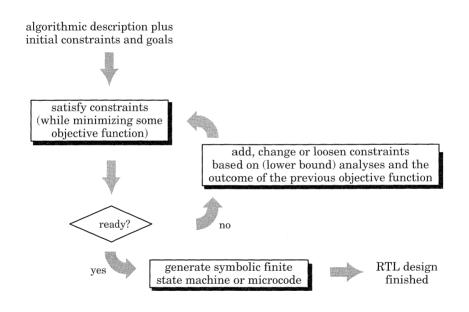

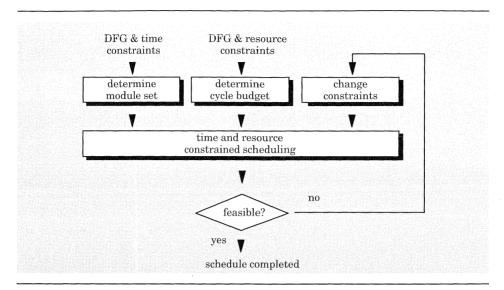

FIGURE 1.2. Design methodology for architectural synthesis.

This leads to the design methodology pictured in Figure 1.2. Starting with the initial goals and constraints imposed on a design, the design process is steered by adding more and more constraints until a design is fully constrained, i.e., specified. For instance, a design with only timing constraints at the beginning of the design process, will become more and more time *and* resource constrained along the synthesis flow by adding resource constraints. So, the initial problem description is modified during the synthesis flow. The synthesis result now relies on the constraints additionally imposed on a design and the ability of the synthesis system to satisfy all the constraints. For that reason, the ability of a synthesis system to satisfy

different combinations of constraints becomes essential in such a design methodology. The role of minimizing objective functions is merely reduced to steering the process of adding constraints; the outcome of an objective function can give an insight in the design space.

The additional constraints can be generated by CAD tools or by user interaction and can be based on (lower bound) design space analyses. It will be shown that lower bound analyses give good insight in the design space, so they can also help to measure the quality of design decisions. To enable a designer to enforce certain synthesis decisions, a synthesis system must be able to deal with different combinations of constraints. The approach of Figure 1.2 has, therefore, the additional advantage that user interaction is smoothly incorporated in the design flow.

# 1.3.4 Methodology considerations

Instead of concentrating on minimizing certain objective functions, the methods and algorithms in this thesis emphasize *lower bound design space* analyses and constraint satisfaction techniques. To obtain a conceptually sound synthesis flow supporting such a methodology, the following considerations must be kept in mind.

- For the *constraint generation*, a designer or a synthesis tool must be able to evaluate the quality and status of a design at any time, to support (interactive) changes of the added constraints. A designer should receive as much helpful information as possible, which can be used to steer certain synthesis tasks, e.g., information that can help to select resources manually. Chapter 3 deals with lower bound analyses, which help a designer or CAD tool to evaluate the quality of a design.

- After observing the current status and the quality of a design, a designer or a tool must be able to enforce certain features of a synthesis solution. Hence an architectural synthesis system should be capable of handling designs on which many constraints of different nature are imposed, i.e., such a system must have powerful *constraint satisfaction* techniques.

Many existing synthesis systems are hampered in dealing with large sets of constraints. Yet a synthesis system should exploit all the constraints that are imposed, as the number of solutions decreases with an increasing number of constraints of different nature. Chapter 2 introduces a low—order polynomial run time algorithm which shows the possibility of taking advantage of different kinds of constraints instead of being hampered by them. The algorithm prunes the search space of schedulers without limiting the solution space when both time and resource constraints are imposed on a design. It is therefore a complementary technique to heuristics.

- The run time efficiency of the different tasks performed by a synthesis system must be as high as possible. However, in order to give a designer maximum flexibility, a designer must also be able to control the trade-off between the solution quality and the run time efficiency of a synthesis task. The tedious task of scheduling is preferably left to a synthesis system and is not performed manually. Architectural synthesis scheduling problems are in general NP-hard, so an optimal solution cannot be guaranteed within acceptable CPU times. However, it can be profitable to spend more CPU time to obtain a (near) optimal solution for critical parts of a design. In Chapter 4, a scheduling algorithm will therefore be presented which offers the possibility of trading off the solution quality against the run time efficiency.

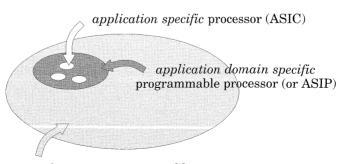

- Eventually, at the end of the synthesis flow, it may occur that a complete datapath consisting of interconnected resources plus timing constraints is enforced by a designer or a synthesis tool, i.e., the design is completely constrained. The remaining task for the synthesis system is then to find a correct schedule and binding scheme. This is actually the starting point of retargetable code generation, see [Paul94] or Chapter 5. So retargetable code generation is a natural part of the design methodology depicted above and even a touchstone of it. If it is not possible to develop a good retargetable code generator, then a design methodology built upon constraint satisfaction is not favorable.

# 1.4 Towards a solution strategy

The discussion in the previous section leads to the hypothesis that a good design methodology is focused on adding constraints to a design by means of analyses and design space explorations until the design space is narrowed down sufficiently to contain only (a few) satisfactory solutions. A design will be more or less completely constrained at the end of such a process. Therefore, the application domain and the *initial* goals and constraints will become less and less 'visible' and are deemphasized along the synthesis flow, because the initial problem description is modified.

This leads to a concept where the classical subtasks of architectural synthesis (selection, scheduling and binding) are not the main steps in the synthesis flow, but reflect merely tentative decisions that can be revoked in a next synthesis step. In this concept, the steps in the synthesis flow are aimed at different aspects of datapath optimizations and trade—offs. So, it must be possible to execute the different synthesis tasks and optimization strategies in an arbitrary way, in an arbitrary order and an arbitrary number of times until a satisfactory solution has been found. Two questions remain: is there a preferable order of synthesis tasks and is the run time efficiency and quality of all the synthesis tools sufficiently large to be invoked repeatedly.

### Best understood subtasks

Literature on architectural synthesis shows that scheduling is one of the best understood subtasks in the field [McFa90]. As to optimality, the classical scheduling problems come in the following two clean forms.

- In time constrained scheduling one is asked to arrange the schedule within a given (maximum) number of clock cycles (the so called cycle budget) while minimizing the cost (mostly given in terms of area) of resource usage.

- In resource constrained scheduling one is asked to arrange the schedule within maximum bounds on the resource usage while minimizing the number of clock cycles.

In real life, a scheduling problem may come as a mixture of those clean forms, and many systems are known to become both time and resource constrained along the way. This is done to achieve a tight performance control, in compliance with the design methodology explained in Section 1.3. Examples are the systems HYPER [Raba90], MSSR [Ishi91], TBS [Rama91], CADDY [Gutb92], Phideo [Verh95] and NEAT [Timm93a], which are time constrained at the beginning of the design flow. The resource constraints are mostly given in terms of the number of instantiations of functional units, because there are many efficient approaches giving a lower bound estimate on the functional area, see [Jain92], [Shar93], [Timm93c] or Chapter 3. The scheduling and functional area estimation tasks can be modelled easily with a so called data flow graph model, see Section 1.5.2, and can be solved efficiently.

#### Flow of subtasks

Because the subtasks mentioned above are so well understood, a logical first step in a solution strategy is to determine the minimal functional area, or the minimal cycle budget in case the resources are given, without considering interconnect and memory costs. Chapter 3 and 4 show that, starting from an initial lower bound estimate of the module set with minimal functional area for a given time constraint, a module selection review can take place until a feasible module set is found. A trade—off can be made between the optimality of the solution and the run time efficiency of such an approach. A good evaluation of such a synthesis task can be obtained: both a lower bound estimate and the area of the resulting set of functional units are available. With these numbers a designer can estimate the quality of the resulting set of functional units.

The number and place of the register files or other memory elements in a datapath partly depend on the bus configuration. A logical next step in the synthesis flow is therefore to trade off functional area against interconnect

area and delay to decrease the total area, while tentatively not considering the memory area. Many synthesis systems try to optimize the interconnect after a schedule is fixed [Pang88] or during scheduling [Bala89], [Berry90]. Some systems cluster operations before a schedule is fixed based on the regularity in a DFG [Note89], [Rao93]. These clusters then reappear in the datapath as clusters of modules which are interconnected through local buses. Clustering can lead to fewer global buses at the expense of more module area.

Such a trade–off should be guided by the regularity in the DFG [Rao92] and estimates of the total functional and interconnect area / delay. These estimates must have a realistic accuracy: because of the run time efficiency it is not desirable to perform a fine–grain placement and routing at the architectural synthesis phase of a silicon compiler, if this task has to be performed many times. Estimations like the one in [Kurd91] try to be run time efficient and yet accurate enough for this purpose, but not much research has yet been done in this field. The insight in the design space can be good, if the trade–off starts with a datapath with minimal functional area and mainly global buses and evolves towards a data path which consists completely of groups ('clusters') of modules with only a few global buses. An additional advantage of such a step in the design flow is that the interconnect delay can be taken into account during later synthesis steps.

A next step in the solution strategy can possibly be memory minimization. A trade—off between memory area and functional / interconnect area can be found in a subsequent step, e.g., by enforcing an ordering between different data transfers and/or by binding some data transfers in advance. By performing the other synthesis tasks iteratively, less memory area can be allocated at the expense of functional and / or interconnect area. As has been said, in a solution strategy like the one described in this section, it should be possible to revoke the different synthesis steps an arbitrary number of times until a satisfactory solution has been reached.

# 1.5 Description of the NEAT design environment

# 1.5.1 Overview of requirements

Despite the diversity in design styles many tasks in the synthesis flow are similar. The previous sections discussed the hypothesis that a good overall design methodology will lead to a more or less uniform solution approach making it unnecessary to write a new synthesis system for each design style. A synthesis system should, nevertheless, allow as much freedom as possible with respect to the way and order in which the subtasks of the synthesis problem are solved.

To solve the architectural synthesis problem as a whole, a collection of interacting tools is needed. This leads to the insight that *software engineering* and *data management* are important aspects of the design environment requirements. Each tool has to retrieve, manipulate and store intermediate synthesis results by using a synthesis data interface. Because synthesis data is shared among different synthesis tools, the data interface should be common to all tools, which makes the maintainability of separate tools, programming efficiency and the preservation of the consistency of synthesis data much easier. On the other hand, each synthesis tool has its own requirements for the synthesis interface. It must be possible to add tool specific data to the interface which is hidden from the data interface of other tools. The interaction between different tools can be achieved by the exchange of intermediate synthesis data accompanied by specific keywords indicating the status of the data. An example is a keyword that states whether it is allowed to change the schedule of operations if the set of resources is altered.

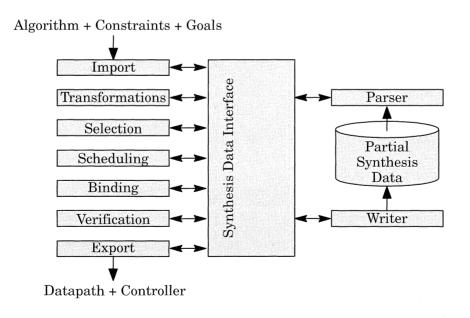

#### 1.5.2 NEAT and its data domains

An object oriented synthesis interface, the *New Eindhoven Architectural* synthesis *ToolBox (NEAT)* written in C++ has been developed in compliance with the requirements of Section 1.5.1; see [Heij94] and Figure 1.3. At the left

$\textbf{Figure 1.3.} \ \ \textbf{The architectural synthesis interface and tools.}$

hand side of the figure, a number of possible synthesis tools, e.g., import, selection, scheduling, export, etc., are given. A parser reads synthesis data from a file and stores it into memory in the synthesis data interface. The interface abstracts the different synthesis tools from the synthesis data by providing access routines to the data.

NEAT offers unlimited extendibility and no restrictions with respect to a synthesis flow or methodology. Three domains of data can be distinguished: a *behavioral*, a *timing* and a *structural* domain. From a theoretical point of view, these domains can be represented by a single domain by labeling timing and structure information to the behavioral data [Jong93]. A separation of the three domains has been decided for the ease of implementing the various synthesis tools and for the ease of representing the synthesis results. NEAT provides, but is not limited to, three design views corresponding to these domains. Other domains of data can be added by adding new views to the interface.

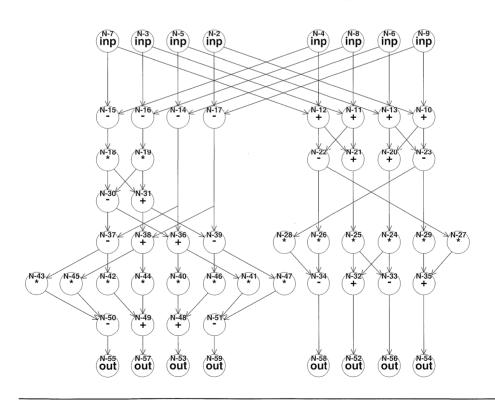

### Behavioral domain

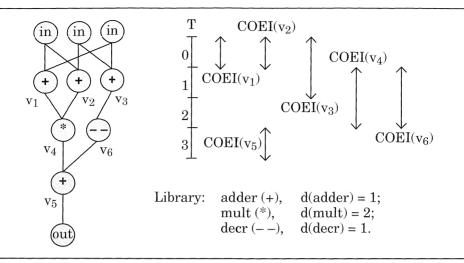

The first domain in NEAT is the behavioral domain, and in this domain ASCIS data flow graphs (DFGs) are used to describe the behavior of a design [Eijnd92]. Data flow graphs are the internal representation of the algorithmic description and can be obtained from hardware description languages by means of data flow analysis. With DFGs it is tried to give a representation of the behavior of a design which contains as much parallelism as possible. Applying synthesis directly to a DFG frees synthesis from the varying nature of input languages and facilitates possible algorithmic transformations. Data flow graphs impose no limitations with respect to architectural solutions. They are, therefore, suitable as a starting point for architectural synthesis.

Although there are a number of DFG models around, the common feature of all those models is that they map certain elementary actions on the vertices of such a graph. Those actions are arithmetic operations like additions, subtractions or multiplications, but also the generation of constants, bit operations like masking and shifting, conditionals, loop controls and memory read / write actions. In the sequel, these actions are called *operations*. The interface of a data flow graph to the outside world is defined by means of input and output vertices.

In addition to the decomposition of algorithms into elementary operations, the DFG model captures the dependencies between those operations. Mostly those dependencies are established by the fact that operations consume values, or 'tokens', produced by other operations. An operation has to be

scheduled in time after the completion of the operations producing the required input values. In this thesis, those precedence relations are called *data dependencies*, although this obscures the fact that the inputs could also be control signals as well and data independent sequencing relations can also exist.

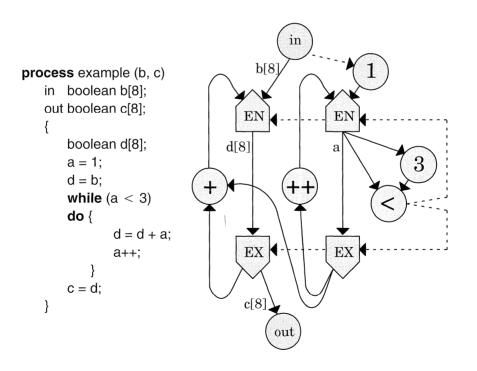

To support the special language constructs like loops and conditionals, vertices with a special execution mechanism have been defined. An example of a data flow graph with such a special construct has been given in Figure 1.4. At the left hand side of that figure, a textual process declaration has been given. The process consists of a loop, which results in entry (EN) and exit (EX) vertices in the DFG. An entry vertex takes the input of one of its input arcs and sends it over its output arc; an exit vertex takes an input token and copies it to one of its output arcs. The choice which arcs are selected depends on a control signal provided to these vertices, see the dashed arcs in Figure 1.4. The left entry and exit vertices pass the values of the variable 'd', while the right entry and exit vertices pass the values of the variable 'a'. For a more elaborate discussion on the ASCIS data flow graph, see [Eijnd92].

FIGURE 1.4. Example of a data flow graph.

## Timing and structural domains

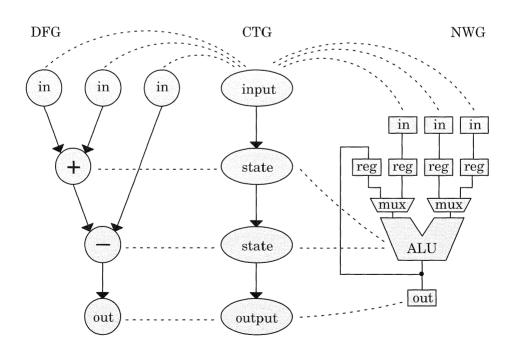

The second and third domain in NEAT are the timing and structural domains respectively. In the *timing domain*, the time behavior of a design is described by a control graph (CTG) which models a finite state machine, see Figure 1.5. In that figure, a DFG has been given at the left hand side, while the corresponding CTG has been given in the middle. Vertices in a control graph represent states, except for the input and output vertices, and edges represent state transitions. the dashed edges between the DFG and CTG in Figure 1.5. denote in which state a certain operation is scheduled. Furthermore, control graphs can be extended with special constructs to explicitly represent conditionals, loops, multiple active states and hierarchy to hint at the controller design.

In the *structural domain*, the datapath of a design is described by a network graph (NWG), see also Figure 1.5. There, the NWG is given at the right hand side, describing the datapath by register transfer level components and their interconnections. The dashed edges to the NWG denote in which states the modules are active and what operations are mapped to them.

FIGURE 1.5. Simplified example of inter-domain relations.

## 1.5.3 Design relations

Between the three domains relationships are established to point out how the different synthesis objects are related. Two important types of relations can be distinguished: intra-domain and inter-domain relations.

The *intra-domain relations* are used to preserve consistency of data within a domain, by means of describing the behavior and interface of vertices by graphs within the same domain. An operation, state vertex or network module can be generated by referring to a graph, inheriting the interface and behavior of that graph. The interface of a graph is described by input and output vertices, the behavior by its contents (vertices and edges), documentation (for standard operations like additions and multiplications), or computer programs (for standard modules like adders, multipliers, RAMs, and so on). Hence intra-domain relations provide support for hierarchical bottom—up and top—down design methods.

The *inter-domain relations* describe the relationships among objects of different design views by means of so called graph links and vertex links. Links can be specified only partially to represent intermediate synthesis results. A *graph link* relates a data flow, control and network graph with each other. Such a link represents a relation like 'this network graph represents the datapath belonging to this data flow graph'. A *vertex link* relates a data flow vertex, control vertices and a network vertex with each other. Such a link denote the fine–grain relations among graphs, like 'this data flow vertex is bound to this network vertex', and / or 'this data flow vertex is scheduled onto these control vertices'. A graphical and simplified example of inter–domain relations has been given in Figure 1.5.

Inside links the kind and status of the relationship they represent can be defined in more detail, which makes it easier for tools to decide how particular links should be used. The links describe the complex and detailed fine—grain relationships separately from the graph descriptions in the different domains. Nevertheless, synthesis information is gently incorporated into the synthesis data. Design analysis tools like formal verifiers, simulators or graphical interactive tools can easily use the links to determine the relationships between behavior, time and structure. In [Hild94], an example of the use of graphical interface tools which are part of the ESCAPE system [Fleu96] has been given. ESCAPE reads the links from the NEAT interface and shows the information contained in the links graphically.

# Chapter

# 2

# **Execution Interval Analysis**

### 2.1 Introduction

In almost any of their formal appearances, architectural synthesis scheduling problems are not solvable in polynomial time, see [Heem90], [Verh91], [Verh95]. For that reason, many heuristical approaches have been investigated; see for typical examples [Girc85], [Park86], [Peng86], [Pang87], [Paul87], [Thom88], and [Camp90]. Under the regime of tight performance control, more and more instances of the problem appear where heuristic approaches render unsatisfactory results, see Chapter 5. A search for exact methods like integer programming (IP) techniques [Hwang91], [Gebo92] and branch—and—bound methods has therefore been initiated.

Exact methods depend on powerful branching and pruning techniques, which are called variable & value selection and domain reduction (or consistency checking) respectively in the field of constraint satisfaction, see for instance [Nuijt95]. One of the important ways to support pruning is the analysis of the *operation execution intervals* (OEIs), for which the following informal definition can be given.

Given some operation v in a DFG, the associated OEI restricts the interval of consecutive clock cycles to which v can be assigned. A classical and conservative, but pessimistic, estimate for the bounds of some OEI, which is applied in most architectural synthesis systems, is given by the 'as soon as possible' (ASAP) and 'as late as possible' (ALAP) values of an operation. These values are obtained by a critical path analysis of the DFG under the assumption of unlimited resources. Such an analysis accounts only for the data dependencies and the delays of the operations in the DFG. In the presence of constrained resources though, i.e., if there are not only timing constraints imposed on a design but also resource constraints, the pruning is still far from satisfactory.

In this chapter a new technique is proposed to enhance the pruning capability of scheduling approaches, by reducing the classical operation execution intervals mentioned above. The reduction is obtained in low–order polynomial time with a bipartite graph matching formulation that exploits both time and

resource constraints. It prunes the search space of schedulers without limiting the solution space, thus enhancing the quality of schedulers. With this technique a synthesis system makes use of all the different kind of constraints that are imposed, instead of being hampered by them. It is therefore a complementary technique to heuristics: if there is much scheduling freedom, then no or hardly any pruning will occur.

This thesis deals with the execution interval analysis first, because it is used throughout the whole NEAT synthesis trajectory and throughout the rest of this thesis as well. For instance, Chapter 4 deals with the scheduling process itself and shows that the matching formulation introduced in this chapter is not only capable of *pruning* the search space. The bipartite matching formulation is also very valuable for *traversing* the search space efficiently, i.e., for the variable & value selection part of a scheduler.

The outline of this chapter is as follows. In Section 2.2, a number of definitions and the formal problem definition of execution interval analysis are given. Section 2.3 starts with considering trivial module libraries: the section considers the case in which there is a one—to—one mapping from operation types to module types. In Section 2.4 the approach is extended to unrestricted libraries allowing for many—to—many mappings. The chapter concludes with experimental results and a discussion in Section 2.5 and 2.6 respectively.

#### 2.2 Definitions

In the sequel of this thesis, the following formal definitions are needed.

# **DEFINITION 2.1.** Data flow graph DFG.

A data flow graph DFG is a 2–tuple (V, E), where V is the set of vertices (operations) and  $E \subseteq V \times V$  the set of arcs representing dependencies between operations.

# **DEFINITION 2.2.** Operation types.

T<sub>O</sub> is the set of operation types in a DFG. An example of an operation type is the addition.

**DEFINITION 2.3.** Operation type function.  $\tau: V \to T_O$  gives for each operation its type.

**DEFINITION 2.4.** Immediate predecessors.  $pred(v) = \{w \in V \mid (w, v) \in E) \text{ for each } v \in V.$

**DEFINITION 2.5.** Immediate successors.  $succ(v) = \{w \in V \mid (v, w) \in E) \text{ for each } v \in V.$

### **DEFINITION 2.6.** Transitive closure.

The transitive closure of DFG is the graph DFG\* = (V, E\*), where E\* = { (v, w) | v, w  $\in$  V and v is connected to w in DFG}.

### **DEFINITION 2.7.** Predecessors.

$\operatorname{pred}^*(v) = \{ w \in V \mid (w, v) \in E^* \} \text{ for each } v \in V.$

### **DEFINITION 2.8.** Successors.

$\operatorname{succ}^*(v) = \{ w \in V \mid (v, w) \in E^* \} \text{ for each } v \in V.$

### **DEFINITION 2.9.** List of cycle steps.

C is an interval from 0 to |C|-1, representing the list of available cycle steps, i.e., the cycle budget.

### **DEFINITION 2.10.** Set of modules.

M is a set of modules. In this thesis, most of the time this set is restricted to functional units. An example of such a set is three adders and two multipliers.

## **DEFINITION 2.11.** Set of module types.

$T_{\rm M}$  is the set of module types, or library. An example of a module type is the carry–lookahead adder type.

It is important to notice the difference between a set of modules and a set of module types, or module library. This difference will be crucial for the execution interval analysis in this chapter.

# **DEFINITION 2.12.** Module type function.

$\xi{:}\;M\to T_M$  gives for each module its type.

# **DEFINITION 2.13.** Mapping from operation types to module types.

$\mu$ :  $P(T_O) \rightarrow P(T_M)$ , where P(X) denotes the power set of X, is a mapping from operation types to module types.  $\mu(ts)$ ,  $ts \subseteq T_O$ , returns the union of module types that can implement some, but not necessarily all, operations from the set of operations whose types are in ts.

Although the definition of  $\mu$  is somewhat peculiar, it is used in this chapter and the next chapter on module selection to facilitate the modelling related to many–to–many mappings of operation types to module types.

# **DEFINITION 2.14.** Trivial module library.

A module library  $T_M$  is trivial if there is a one–to–one mapping of operations to modules types, i.e., if  $|\mu(\{\tau(v)\})|=1$  and  $|\mu^{-1}(\{m\})|=1$  for all  $v\in V$  and  $m\in T_M$ . In case of such a library, the delay of an operation is known before scheduling.

### **DEFINITION 2.15.** Unrestricted module library.

A module library  $T_M$  is called unrestricted if it is not trivial. Such a library is especially interesting if  $|\mu(\{\tau(v)\})| > 1$  for some  $v \in V$ .

### **DEFINITION 2.16.** Delay of a module type.

d:  $T_M \to Q^+$ , where  $Q^+$  is the set of positive rational numbers, gives the minimal fractions of cycles, i.e., the delay, a module needs to execute an operation.

# **DEFINITION 2.17.** Minimal execution delay of an operation.

In case of a trivial module library, see Definition 2.14, the minimal execution delay of an operation  $d_{min}(v)$  equals d(m), with  $\{m\} = \mu(\{\tau(v)\})$ . In case of an unrestricted module library, see Definition 2.15, the minimal execution delay  $d_{min}(v)$  of an operation v equals  $\min_{m \in \mu(\{\tau(v)\})} d(m)$ .

# **DEFINITION 2.18.** Data introduction interval of a module type.

dii:  $T_M \to \mathbb{N}^+$ , where  $\mathbb{N}^+$  is the set of positive natural numbers, returns the data introduction interval (or restart time), which is the minimal number of cycles required between the data arrivals for two successive executions of different operations on a module.

A pipelined module can have a larger delay than data introduction interval. For a module that can be chained, the delay is smaller than the data introduction interval, which equals one clock cycle in this case.

If nothing else is said, a next instantiation of the DFG takes place only after the DFG is finished completely, i.e., the delay and dii of a DFG are equal. Furthermore, if nothing else is said, the DFG is considered to be an acyclic graph without control constructs. In that case, an operation in a DFG can be executed if at least one token, i.e., value, is available on each of its input arcs, resulting in the production of a token on each of its output arcs.

The assumptions above are made for reasons of simplicity. For instance, control constructs are handled by the implementations of the methods, but are not treated explicitly in this thesis. For most methods it is not difficult to take cyclic DFGs into account as well. In Chapter 5, for instance, a loop model is used in which the delay and dii of a DFG can differ.

# **DEFINITION 2.19.** Schedule interval of an operation.

The schedule interval  $\phi(v) = [\phi_1(v), \phi_2(v)]$  of an operation  $v \in V$  is given by the start time  $\phi_1(v)$  and the completion time  $\phi_2(v)$ , such that the operation is being executed in that interval. Non preemptive scheduling is assumed, which implies that the delay, i.e., processing time, of a scheduled operation v equals  $\phi_2(v) - \phi_1(v)$ . Depending on the binding of an operation to a module, the delay of an operation can have different values.

## **DEFINITION 2.20.** Schedule.

A schedule  $\phi$  assigns to each operation  $v \in V$  a schedule interval  $\phi(v)$ . A schedule is called feasible, if all precedence, resource and time constraints for the DFG are met.

### **DEFINITION 2.21.** Set of feasible schedules $\Phi$ .

In the sequel only the set of *feasible* schedules  $\Phi$  is considered, in which all precedence, resource and time constraints for a given DFG are met. Thus any  $\phi \in \Phi$  is by definition a feasible schedule. Note that this set may be empty for certain compositions of constraints.

**DEFINITION 2.22.** Classical 'as soon as possible' start time of an operation. Let the set of constraints associated with  $\Phi$  consist of precedence constraints only. The classical 'as soon as possible' start time CASAP(v) of an operation  $v \in V$  is defined by: CASAP(v) =  $\min_{\Phi \in \Phi} \Phi_1(v)$ .

**COROLLARY 2.1.** Polynomial calculation classical 'as soon as possible' time. Consider an acyclic data flow graph. Then the CASAP(v) for all  $v \in V$  can be determined recursively in O(|V| + |E|):

$$CASAP(v) = \begin{cases} 0 & \text{if } pred(v) = \emptyset \\ \max_{w \in \ pred(v)} \left( CASAP(w) + d_{min}(w) \right) & \text{if } pred(v) \neq \emptyset \end{cases}$$

**Definition 2.23.** Classical 'as late as possible' completion time.

Let the set of constraints associated with  $\Phi$  consist of precedence constraints and a timing constraint only. The classical 'as late as possible' completion time CALAP(v) of an operation  $v \in V$  is defined by: CALAP(v) =  $\max_{\Phi \in \Phi} \Phi_2(v)$ .

**COROLLARY 2.2.** Polynomial calculation classical 'as late as possible' time. Consider an acyclic data flow graph. Let the time constraint be defined by the list of clock cycles C. Then the CALAP(v) for all  $v \in V$  can be determined recursively in O(|V| + |E|):

$$CALAP(v) = \begin{cases} & \text{if } succ(v) = \emptyset \\ \min_{w \in succ(v)} \left( CALAP(w) - d_{min}(w) \right) \text{ if } succ(v) \neq \emptyset \end{cases}$$

**DEFINITION 2.24.** Classical operation execution interval.

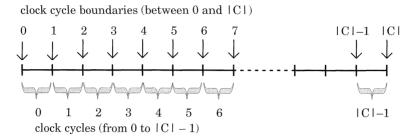

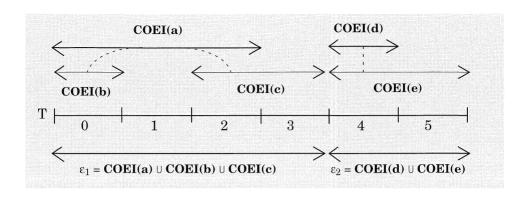

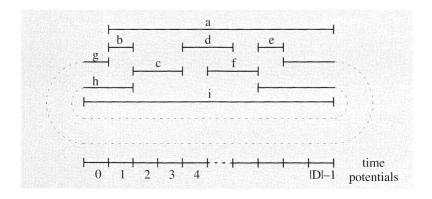

The CASAP and CALAP values are rational numbers to allow the recursive calculation of these values in case the operations can be chained: in such a case not all of the CASAP and CALAP values are on clock cycle boundaries. Figure 2.1 points out the difference between clock cycles and clock cycle boundaries. In contrast to those values the classical operation execution interval COEI(v) of an operation  $v \in V$  is defined by an interval of clock cycles: COEI(v) = [|CASAP(v)|, [CALAP(v) - 1]].

FIGURE 2.1. Difference between clock cycles and cycle boundaries.

In the previous definitions, no resource constraints were part of the set of constraints for  $\Phi$ . In the following three definitions, resource constraints are part of the set of constraints, which leads to subtle differences in the definitions.

**DEFINITION 2.25.** 'As soon as possible' start time of an operation.

Let the set of constraints for  $\Phi$  consist of precedence constraints and resource constraints. Then the 'as soon as possible' start time ASAP(v) of an operation  $v \in V$  is then defined by:

$$ASAP(v) = \min_{\phi \in \Phi} \phi_1(v).$$

**DEFINITION 2.26.** 'As late as possible' completion time of an operation.

Let the set of constraints for  $\Phi$  consist of precedence constraints, timing constraints and resource constraints. Then the 'as late as possible' completion time ALAP(v) of an operation  $v \in V$  is defined by:

$$ALAP(v) = \max_{\phi \in \Phi} \phi_2(v).$$

# **DEFINITION 2.27.** Operation execution interval.

The operation execution interval OEI(v) of an operation  $v \in V$  is defined by the following interval of clock cycles: OEI(v) = [[ASAP(v)], [ALAP(v) - 1]].

An important difference between a COEI and OEI is the fact that the CASAP and CALAP values can be calculated in polynomial time, while the ASAP and ALAP values can not be calculated in polynomial time in the general case. We will return to this issue later on.

Because the ASAP, ALAP and OEI can, in general, not be calculated in polynomial time, the determination of conservative estimates will be discussed in this chapter. For that reason we introduce the following definitions for the conservative estimates of these values.

**DEFINITION 2.28.** Conservative estimate of the 'as soon as possible' time. The conservative estimate  $\overline{ASAP}(v)$  of an operation  $v \in V$  is an estimate of ASAP(v), satisfying  $CASAP(v) \leq \overline{ASAP}(v) \leq ASAP(v)$ .

**DEFINITION 2.29.** Conservative estimate of the 'as late as possible' time. The conservative estimate  $\overline{ALAP}(v)$  of an operation  $v \in V$  is an estimate of ALAP(v), satisfying  $ALAP(v) \leq \overline{ALAP}(v) \leq CALAP(v)$ .

**DEFINITION 2.30.** Conservative estimate of operation execution interval. The conservative estimate  $\overline{OEI}(v)$  of an operation  $v \in V$  is an estimate of  $\overline{OEI}(v)$ , defined by the following interval of clock cycles:  $\overline{OEI}(v) = \lceil |\overline{ASAP}(v)|, \lceil \overline{ALAP}(v) - 1 \rceil \rceil$ .

**DEFINITION 2.31.** Execution interval analysis problem.

Consider an acyclic DFG, a set of modules M on which the operations in the DFG must be mapped, and a list of cycles C, forming the time constraint of the DFG. Find the OEI(v) for each operation  $v \in V$ .

In general, the problem of Definition 2.31 is not solvable in polynomial time, otherwise the accompanying scheduling problem would be solvable in polynomial time as well. Informally, the accompanying scheduling problem is to find a feasible schedule from the set  $\Phi$ . The formal definition is given in Definition 4.1 in Chapter 4.

The proof for the fact that the problem of Definition 2.31 is not solvable in polynomial time is as follows. After solving the execution interval analysis problem of Definition 2.31 for the first time, one operation can be selected and scheduled within its OEI. According to the execution interval analysis, some schedule must exist with that schedule interval for the selected operation. The execution interval analysis can be run a second time, and a second operation can be selected and scheduled within its renewed OEI. This iteration can be continued until all operations are scheduled. Thus, if the analysis problem of Definition 2.31 could be solved in polynomial time, the scheduling problem of Definition 4.1 could be solved in polynomial time as well.

Because the OEIs cannot be calculated in polynomial time, the estimates  $\overline{OEI}(v)$  are calculated for all operations  $v \in V$ , such that the properties in Definition 2.28 and 2.29 are fulfilled and  $|\overline{OEI}(v)|$  is as small as possible. The size of the  $\overline{OEI}$ s in comparison to the COEIs determines the obtained pruning of the search space, i.e., the obtained domain reduction.

#### 2.3 Trivial module sets

#### 2.3.1 Overview

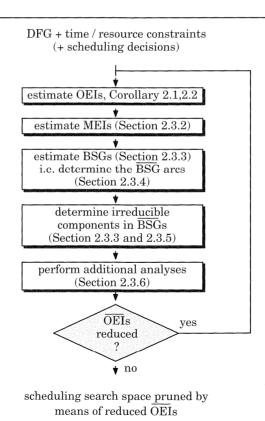

The basic execution interval analysis algorithm explained in the following subsections is meant for *trivial* module sets, see Definition 2.14. In Figure 2.2, the flow of the execution interval analysis is depicted. In this section, the important steps in the analysis will be mentioned, without the exact details. The purpose of this overview is to show where the different algorithms explained in the remainder of this chapter fit in the analysis flow. The purpose is not to explain what kind of actions the different algorithms perform in detail.

In case of a  $\mathit{trivial}$  module set, resource conflicts can occur for each separate module type  $m \in T_M$ , for a given DFG with time and resource constraints. To take these resource conflicts into account, two (related) sets of intervals for each module type are calculated.

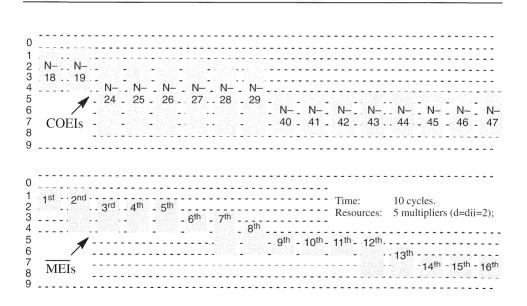

FIGURE 2.2. Flow of the execution interval analysis of Section 2.3.

First of all, for each module type  $m \in T_M$ , the operations  $W_m \subseteq V$  are identified that can be executed on type m. So, the set  $W_m$  consists of operations that may have resource conflicts with each other. For any such operation an  $\overline{OEI}$  is determined. In the first iteration of the algorithm of Figure 2.2, the  $\overline{OEI}$ s are all equal to the corresponding COEIs.

If a next iteration takes place, not all  $\overline{OEI}s$  are equal to the corresponding COEIs anymore, i.e., one or more  $\overline{OEI}s$  will be reduced. So, in the second and subsequent runs of the algorithm of Figure 2.2, the critical path analysis uses the latest determined  $\overline{ASAP}$  and  $\overline{ALAP}$  values and not the values determined by the Corollaries 2.1 and 2.2.

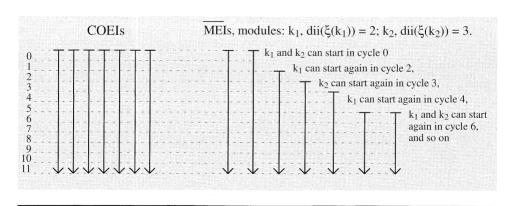

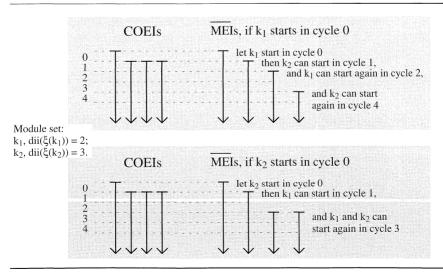

Secondly, in order to account for the resource constraints, a set with cardinality  $|W_m|$  of so called  $module\ execution\ intervals\ (MEIs)$  is calculated. To be more precise, a set of conservative estimates  $\overline{MEIs}$  of those MEIs is determined. Within each MEI, some module of type m has to execute some operation  $v \in W_m$ . The exact definition of an MEI will be presented in the next section in Definition 2.33.

A necessary condition for an operation  $v \in W_m$  to be executed on a module of type m is that its  $\overline{OEI}$  must have sufficient overlap with some  $\overline{MEI}$ , i.e., there must be an overlap which is at least as long as the execution delay d(m). Consequently, if the number of cycles of a  $\overline{MEI}$  is equal to d(m), then some module must start the execution of some operation  $v \in W_m$  in the first cycle of that  $\overline{MEI}$ . In computing the  $\overline{MEI}s$ , not only the  $\overline{OEI}s$  are used, but also the bound on the number of modules of type m and the data introduction interval dii(m). It will be shown how additional pruning of the  $\overline{OEI}s$  can be derived from information contained in the  $\overline{MEI}s$ .

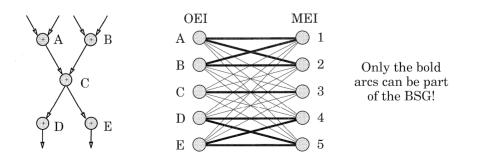

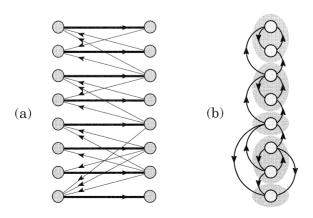

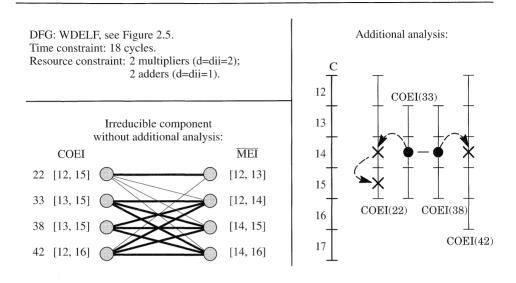

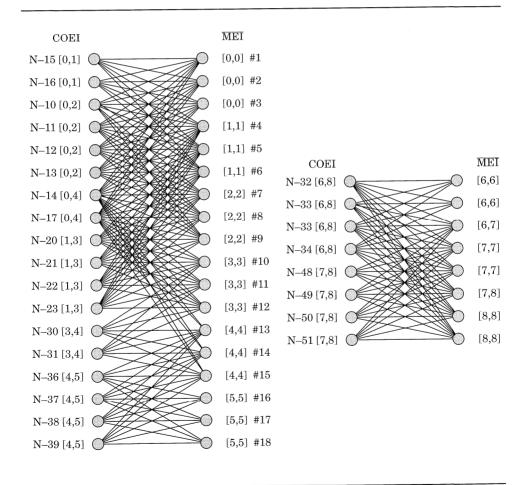

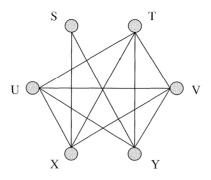

The OEIs and MEIs are used to construct a *bipartite schedule graph* (BSG), which is a bipartite graph with the sets of OEIs and MEIs establishing the required pair of vertex sets. The relation associated with the arcs of a BSG is defined by sufficient overlap of OEIs and MEIs. A necessary condition for the existence of a schedule is the existence of a *complete matching* in the BSG.

Bipartite graphs posses a unique canonical decomposition of their arc set in terms of so called *irreducible components* [Dulm63]. It is shown that arcs outside these components can be removed from the BSG without removing any feasible schedule from the solution space. As a consequence  $\overline{\text{OEI}}$ s can be narrowed, thus reducing the search space without loss of completeness.

#### 2.3.2 Module execution intervals

Because resource conflicts occur for each module type separately in case of trivial module sets, recall Definition 2.14, we consider an arbitrary module type  $m \in T_M$ . Assume that  $K_m \subseteq M$  is the set of modules of type m which can execute simultaneously, i.e.,  $K_m = \{k \in M \mid \xi(k) = m\}$ . The set of operations  $W_m = \{v \in V \mid \{\tau(v)\} = \mu^{-1}(\{m\})\}$  identifies those operations executable by modules of type m. In the sequel the index 'm' is dropped wherever possible. Thus, if nothing else is said, W is the set of operations to be executed by the set K.

## Formal definition

For the definition of module execution intervals, assume a schedule  $\phi \in \Phi$  is given. The schedule  $\phi$  induces a notion of a *partial* order on the set W by ordering the set according to the value  $\phi_1(v)$  for any  $v \in W$ . An ordering based on the values  $\phi_1(v)$  for any  $v \in W$  is not linear, because some operations might have equal start times.

However, as will be seen shortly, we need a linear ordering based on the start times of operations, to be able to define the MEIs. A linear ordering can be achieved by breaking ties on the start times arbitrarily, which is expressed by Definition 2.32. In that definition, an arbitrary linear ordering denoted by  $\ll$  is introduced, which can be interpreted as an assignment of a unique number to every operation  $v \in W$ .

**Definition 2.32.** Linear ordering of operations induced by a schedule. Let  $\leq$  represent an arbitrary linear ordering on W. Given a schedule  $\phi \in \Phi$ ,  $<_{\phi}$  is a linear ordering relation defined by:

$$\begin{picture}(20,0)(0,0) \put(0,0){\ov} \put(0,0){\ov}$$

If  $\phi_1(v) = \phi_1(w)$  then  $\phi_2(v) = \phi_2(w)$  as well, because we are considering trivial module sets for which the delay of all operations  $v \in W$  are the same. As  $\prec_{\phi}$  is a linear ordering it can be used to assign an integer value  $i \in [1, |W|]$ , to any operation  $v \in W$ . This is captured by defining a bijective function  $\pi_{\phi}$ :  $[1, |W|] \to W$ . Thus  $\pi_{\phi}(i)$  is the  $i^{th}$  operation in the linear order induced by the schedule  $\phi$ , and i can be interpreted as the 'operation number' denoting the 'position' of operation  $\pi_{\phi}(i)$  in the schedule  $\phi$ . It is now possible to formally introduce the notion of a module execution interval.

## **DEFINITION 2.33.** Module execution interval MEI.

Consider the set of operations from W assigned to the value  $i \in [1, |W|]$  over the set of all schedules  $\Phi$ . Furthermore, let  $\phi_1(i)$  and  $\phi_2(i)$  be the short hand notation for  $\phi_1(\pi_{\phi}(i))$  and  $\phi_2(\pi_{\phi}(i))$  respectively, i.e.,  $\phi_1(i)$  and  $\phi_2(i)$  are the start

and completion times of the  $i^{th}$  operation  $v \in W$  in the schedule  $\phi \in \Phi$ . Then MEI(i) is defined by the following interval of clock cycles:

$$MEI(i) = \left[ M_1(i), \ M_2(i) \right] \ = \left[ \ \left[ \ \min_{\varphi \ \in \ \Phi} \ \varphi_1(i) \ \right] \ , \ \left[ \ \max_{\varphi \ \in \ \Phi} \ \varphi_2(i) \ - \ 1 \ \right] \ \right].$$

Note that Definition 2.33 is equivalent to Definition 2.27. For any schedule  $\phi \in \Phi$ , the schedule interval of the  $i^{th}$  operation must be within the interval of clock cycles of MEI(i). Note that for different schedules, different operations can be the  $i^{th}$  operation. So, an MEI does not have to be equal to some OEI. Note also that the arbitrary ordering in Definition 2.32 does not have an impact on the definition of any MEI.

Furthermore, the number of MEIs is equal to the number of operations. The length of a MEI indicates a kind of 'freedom' for the set of modules K: within the interval, some module  $k \in K$  must execute some operation  $v \in W$  which can be the  $i^{th}$  operation in a schedule. If the number of cycles in some MEI(i),  $i \in [1, |W|]$ , equals the execution delay, i.e.  $|MEI(i)| = \lceil d(m) \rceil$ , then some module from K must start an execution in the first cycle of MEI(i). This notion of freedom is similar to the freedom expressed by the length of an OEI: if  $|OEI(v)| = \lceil d(m) \rceil$  for any  $v \in W$ , then operation  $v \in W$ , then operation  $v \in W$  cannot be scheduled in more than one way.

Note also that a MEI is not related to a specific module if |K| > 1. Nor is it related to some specific operation  $v \in W$  like the OEIs are. Furthermore, the MEIs are strictly ordered: the first time some module must execute an operation lies in MEI(1), the second time this must happen lies in MEI(2), etc. Consequently we can identify the MEIs and their ordering by their indexes.

## Conservative estimates

Unfortunately, it is not possible to calculate the exact bounds of the MEIs in polynomial time, otherwise the existence of a feasible schedule under given time and resource constraints could be decided in polynomial time and the scheduling problem would be solvable in polynomial time. The reason is simple: if the set  $\Phi$  is empty, then the MEIs are undefined and cannot be determined. If one can determine the MEIs, then the set  $\Phi$  is not empty. So, one has to resort to estimates of the MEIs which do not limit the solution space. For this reason the estimates have to satisfy the following definition.